High density interconnect (HDI) printed circuit boards (PCBs) utilize tighter trace/space to enable higher component density and more routing channels. To facilitate routing dense designs while controlling costs, 2+N+2 stackups are often adopted using microvias to transition between layers.

This article provides guidelines on 2+N+2 HDI stackup design, examining layer configurations, material selections and key considerations for maximizing performance. Best practices for minimizing via stubs, maintaining impedance control and handling power delivery are also covered.

HDI Stackup Overview

A 2+N+2 stackup contains:

- 2 outer signal layers

- N number of internal signal layers

- 2 “low loss” plane layers placed strategically within the stackup

This cost-optimized arrangement provides a balance of signal routing, shielding, power delivery and thermal conduction.

Layer Planning

Careful planning of the 2+N+2 layer stackup ensures all design requirements are adequately met.

Layer Count

The number of layers (N) is selected based on routing density needs and lane count requirements for high speed interfaces. Layer transitions through micro/blind vias minimizes via stub length.

Layer Order

Internal layer order has implications for shielding, power delivery and heat dissipation that must be considered. Tradeoffs are usually required.

Plane Layers

Strategic placement of the two plane layers helps control costs while providing power, shielding and mechanical stability where needed most.

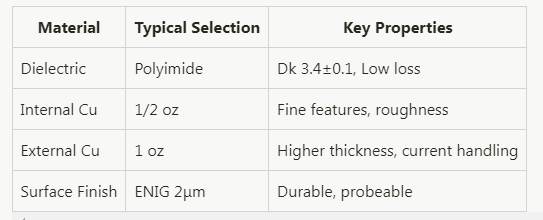

Material Selection

HDI designs require specialized materials to enable fine features reliably while controlling costs.

Dielectrics

Low loss, tight tolerance dielectrics with Dk values under 3.5±0.1 allow microvia stacking while ensuring impedance control and signal integrity. Common options:

- Polyimides (HT)

- FR408HR

- Isola 370HR

Copper

1⁄2 oz copper foil is standard for HDI layers to optimize line width/space while minimizing surface roughness. 1oz copper may be used for thicker outer layers requiring higher current.

Surface Finishes

ENIG or Immersion silver provide durability while minimizing thickness (2–4μm) for the fine pad/via structures used. These finishes also facilitate probe inspection.

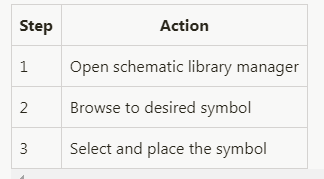

[Table summarizing typical HDI board material selections]

Transmission Lines

Controlling matched impedance transmission lines enables multi-GHz signals on HDI designs.

Trace Geometry

With 1⁄2 oz copper, trace width and space of 3/3 mils is typical. This facilitates 50Ω lines using standard HDI dielectrics. Line width may taper when transitioning layers.

Differential Pairs

Length matching between pairs controls skew. Serpentine routing or meandering helps match physical length. Minimum bending radius rules apply.

Vias

Microvias (0.2mm diameter or under) allow dense via transitions between layers with minimal stubs. Laser drilled through hole vias are still used sparingly for connectivity to thicker multilayer portions.

[Figure showing example controlled impedance traces with length matching and microvia transitions]

Power Distribution

Distributing power across HDI designs brings challenges of high current density and minimizing plane splits.

Power Planes

The 2 “low loss” plane layers are typically used for power distribution to shield signals and serve as low impedance AC current returns. Power nets may still require supplementary polygons on signal layers.

Decoupling

Given narrow power layers, dense passive decoupling placements are needed adjacent to each IC to combat inductance and supply noise. Microvias connect surface caps down to the low loss plane layers.

Thermal Considerations

High power density requires careful thermal analysis with placement optimized to avoid hotspots. Careful component selection together with sufficient vias to inner plane layers also helps dissipate heat.

Design Guidelines and Rules

To aid reliable fabrication and assembly at acceptable yields, design guidelines and rules must be applied during layout.

Routing

- Match line lengths and geometries for differential pairs

- Adhere to microvia stub length maximums

- Breakout blind/buried vias cleanly allowing for annular ring tolerances

Planes

- Minimize plane layer splits

- Thermally balance power dissipation

- Include guest islands in planes for decoupling caps

Manufacturing

- Apply fabrication shop DRC rules

- Set adequate manufacturing tolerances

- Accommodate via aspect ratio limits

Following these guidelines improves manufacturability while also enhancing electrical performance.

Conclusion

A 2+N+2 stackup using microvias and HDI design techniques allows complex, high density PCBs to be manufactured reliably. By adopting the material selections, planning principles and design guidelines covered in this article, engineers can fully utilize this stackup to balance functionality, performance and cost.

Careful layer stack planning together with controlled impedance lines, appropriate decoupling and thermal considerations enables the practical implementation of multi-gigabit systems. As data rates increase and packages shrink, 2+N+2 HDI PCBs will only become more widespread across electronics sectors.

Frequently Asked Questions

Why are low loss dielectrics important for HDI stackups?

Low loss dielectrics with tight dielectric constant (Dk) tolerances enable controlled impedance lines essential for multi-gigabit data lanes. Low loss also ensures signal integrity by minimizing attenuation at RF frequencies.

What considerations influence the selection of internal layer count?

Primary drivers for internal layer count selection include:

- Routing density requirements — more lanes and tighter geometries need more layers

- Achieving target component placement density and footprint efficiency

- High speed interface lane count and routing

- Overall board thickness / rigidity targets

How can I minimize reflection and insertion loss on HDI lines?

Reflections distort signals, cause EMI and increase insertion loss which degrades signal integrity. Controlling line impedance, minimizing discontinuities, length matching, proper termination schemes and using low-loss dielectrics all help reduce reflections and insertions loss.

Why does having a reference plane above and below each signal layer help?

Closely spaced reference planes on adjacent layers provide front-to-back shielding that contains electromagnetic (EM) fields within the dielectric. This prevents crosstalk coupling between traces while also allowing wider lines with better impedance control due to the stronger EM field containment.

What typical features indicate a PCB is manufactured with HDI technology?

Typical giveaways are trace/space ≤ 6 mil with microvias visible between layers under X-ray. HDI designs also often have higher component densities, fine precision manufacturing tolerances, laser via drilling and specialized materials used.